在VScode里搭建舒服的Verilog开发环境

2025-08-07

一、需要安装的插件汇总

vscode本身是不支持Verilog语言开发的,要想在vscode中舒服的编写Verilog源码,需要安装如下插件:

Chinese(simplified)

Material Icon Theme

Verilog-HDL/SystemVerilog

Verilog Highlight

Ctags Support

verilog-utils

Verilog_Testbench

二、插件安装方法

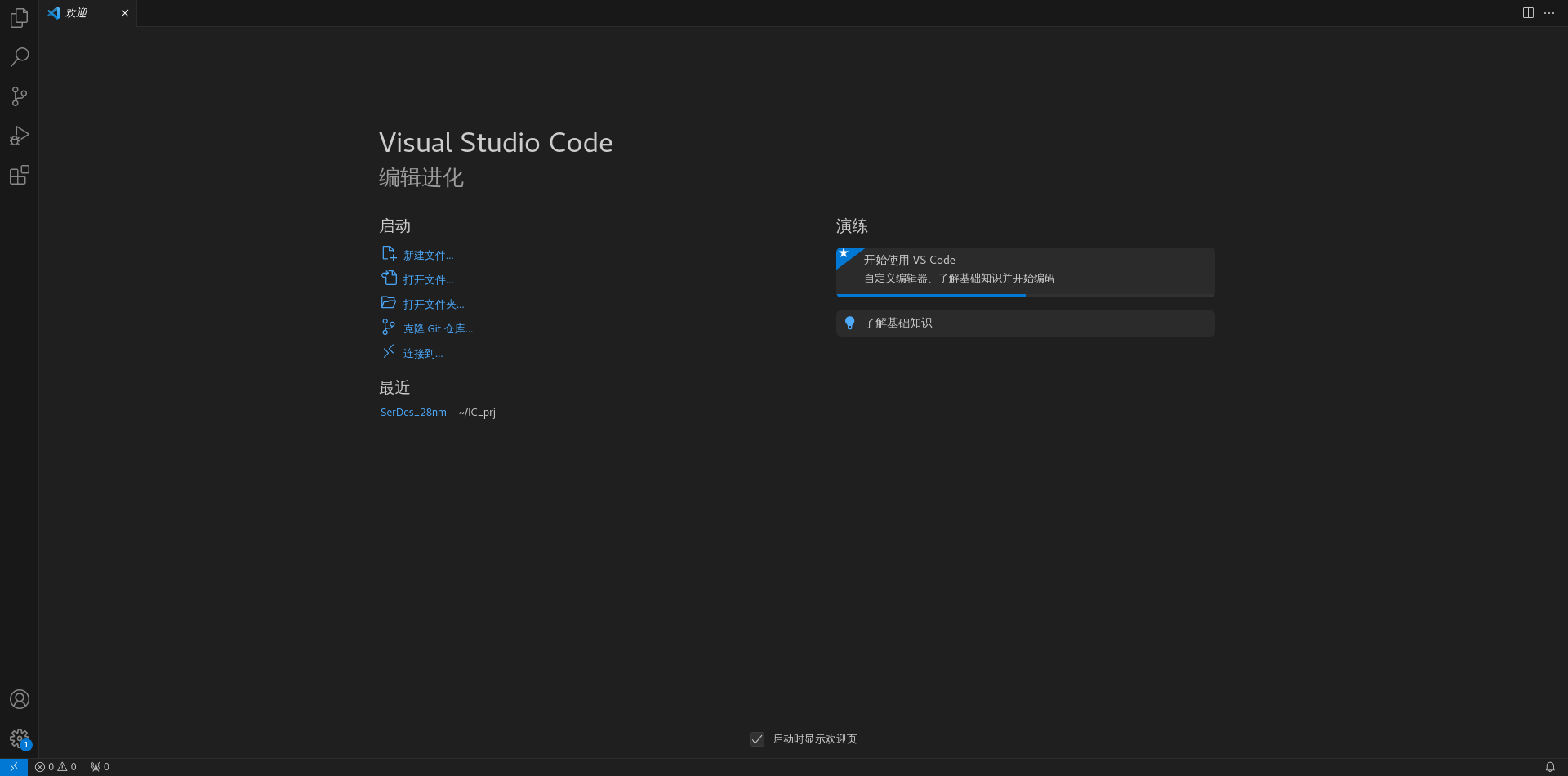

1)当我们安装好VScode,第一次打开时,界面是这样的

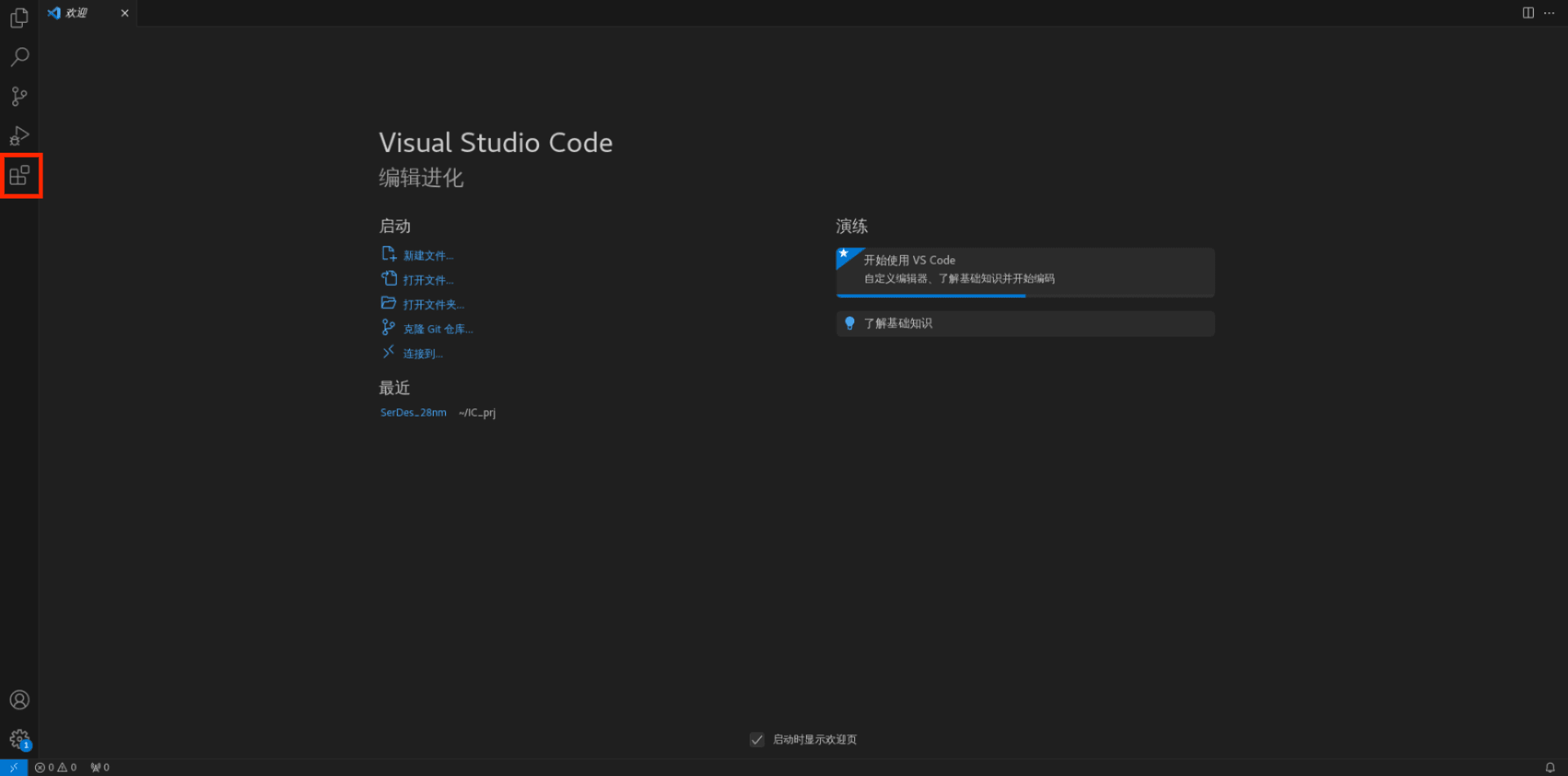

2)在左边状态栏找到extensions选项

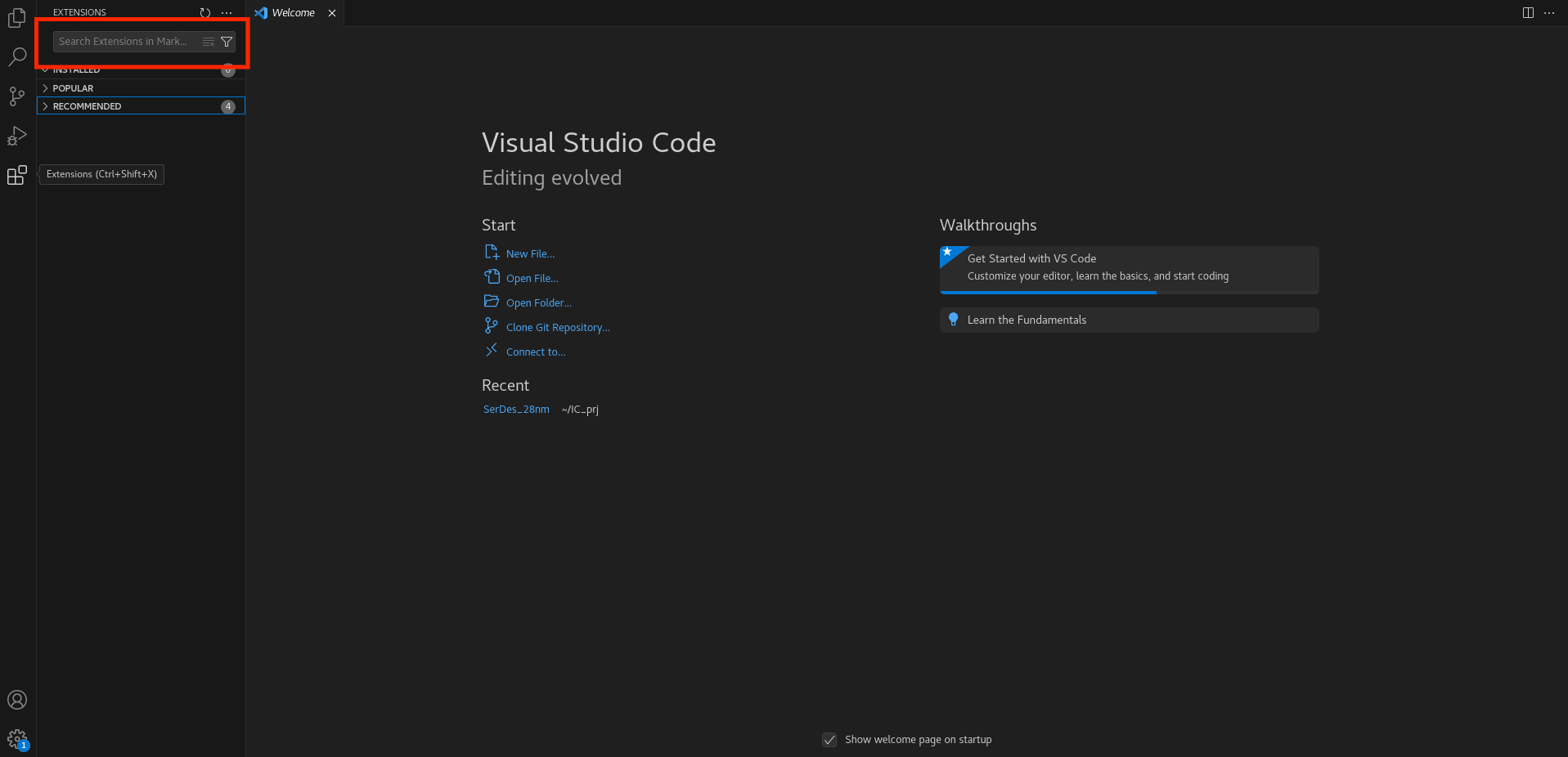

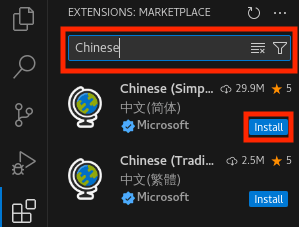

3)在搜索框中输入你想要寻找的插件的名称,这里以汉化插件举例,搜索Chinese

4)选择第一个插件Chinese (Simplified),点击Install

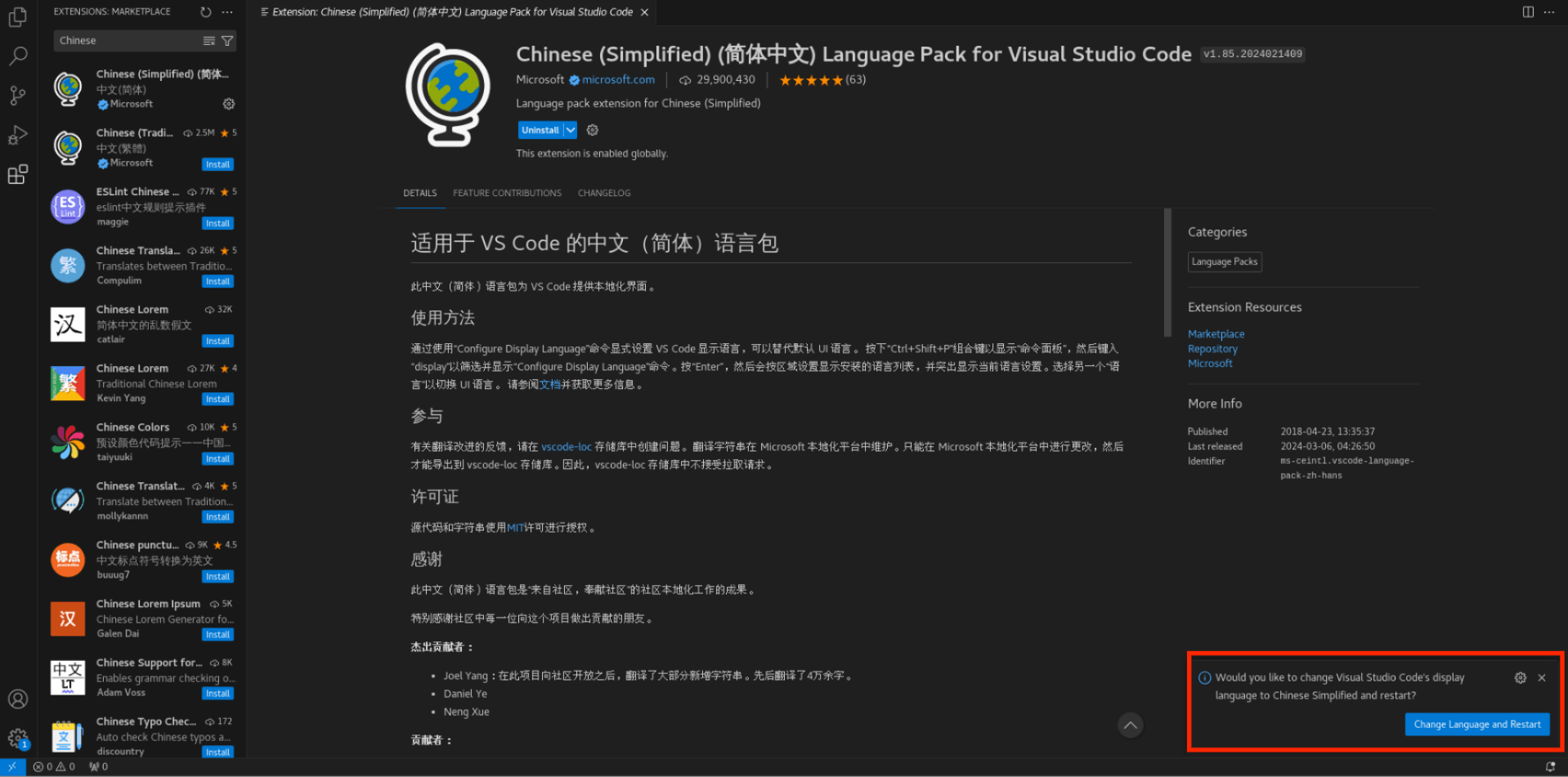

5)在Install完成后,VScode右下角会弹出一个提醒,大致意思就是检测到安装了汉化插件,是否立即重启VScode将英文都替换为中文,我们点击Change Language and Reboot

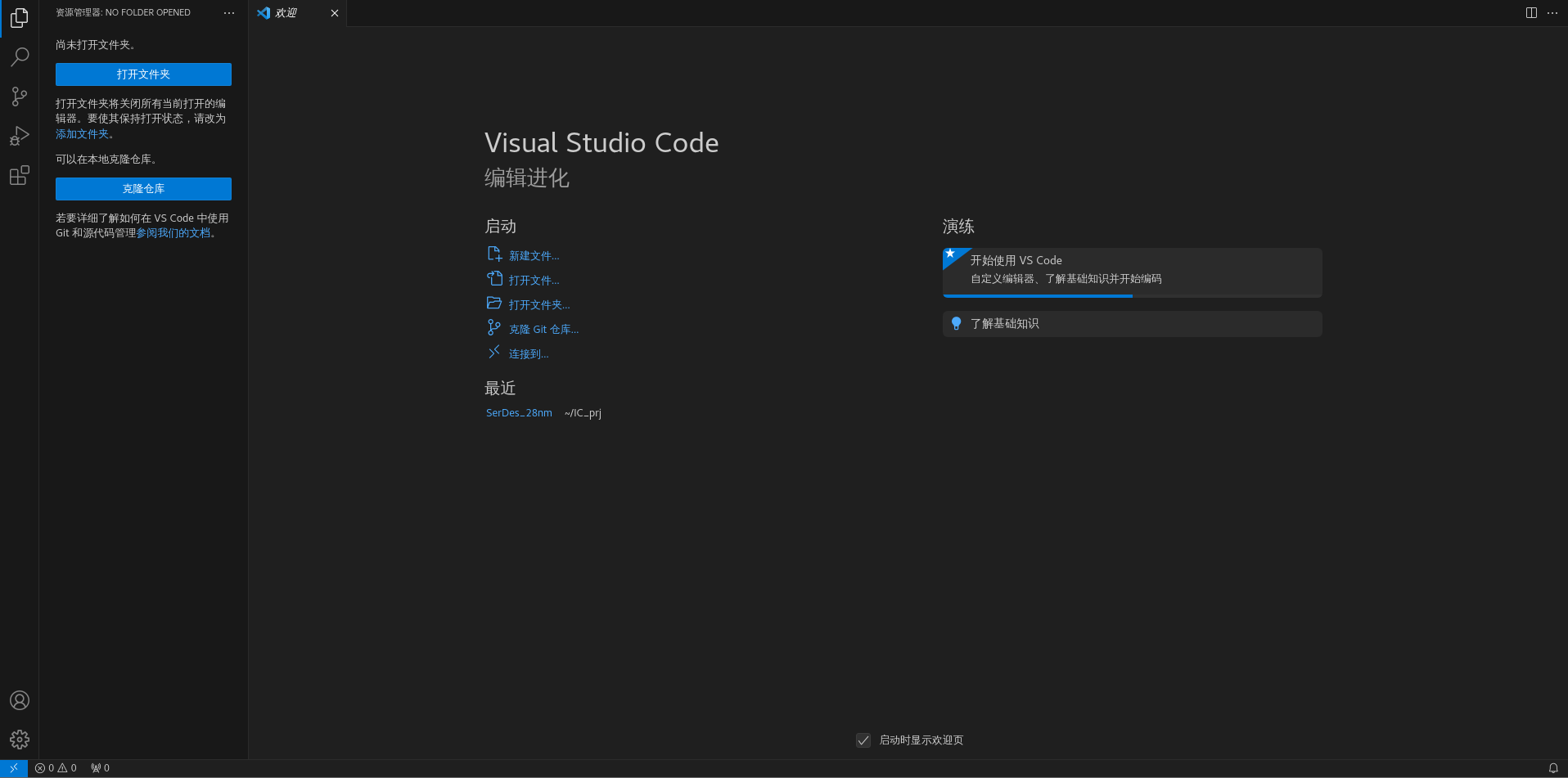

6)再次打开VScode,会发现界面已经都变成中文了,其它的插件也照葫芦画瓢Install

三、各插件介绍

3.1、Chinese(simplified)

3.1.1 插件图标与名称

3.1.2 插件功能

汉化VScode界面

3.1.3 插件用法

无需额外操作,即装即用

3.2、Material Icon Theme

3.2.1 插件图标与名称

3.2.2 插件功能

文件管理器的图标包

3.2.3 插件用法

无需额外操作,即装即用

3.3、Verilog-HDL/SystemVerilog

3.3.1 插件图标与名称

3.3.2 插件功能

这个插件提供了绝大部分Verilog开发环境的基础功能,例如:

代码高亮

简单语法自动补全

静态语法检查(需要自己配置lint)

Ctags功能集成(需要自己配置Ctags Path)

自动补全

文档符号大纲

鼠标悬停显示代码声明

CTRL+鼠标点击跳转到代码声明

自动实例化模块

Language Server(实验性功能)

代码自动格式化(实验性功能)

3.3.3 插件用法

3.3.3.1 Ctags配置(这里只介绍CentOS7系统下源码安装Ctags)

1)下载安装Ctags

# 克隆Ctags安装包到本地

$ git clone git@github.com:universal-ctags/ctags.git

# 切换到安装包路径下

$ cd ctags

# 运行脚本生成congigure

$ ./autogen.sh

# 运行configure,可以选择安装位置

$ ./configure --prefix=/where/you/want # defaults to /usr/local

# 运行make,这一步可能要花一点时间

$ make

# 安装,最好以管理员权限进行安装,切换到root用户或者sudo

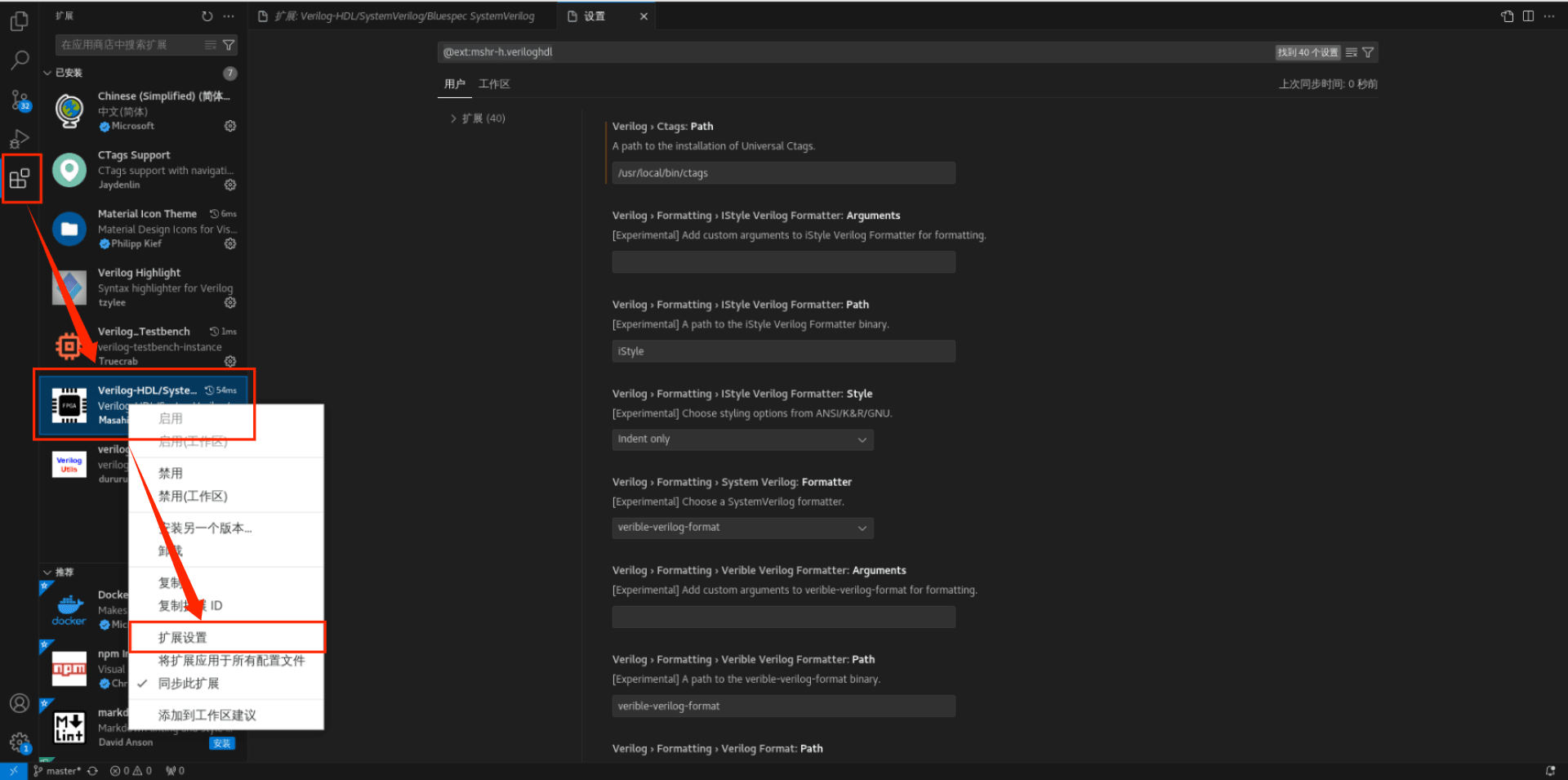

$ make install # may require extra privileges depending on where to install2)打开VScode,点击扩展,右键Verilog-HDL/SystemVerilog插件,选择扩展设置

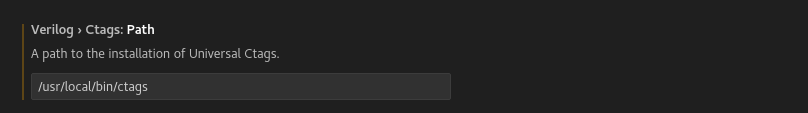

3)找到Verilog>Ctags:Path,修改为Ctags的安装路径

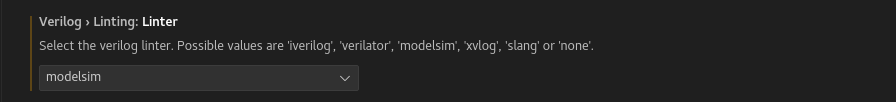

3.3.3.2 静态语法检测linter设置

好像每种linter都会有明明能运行的代码,但是会标红的问题,目前笔主用的是modelsim,大部分情况还可以

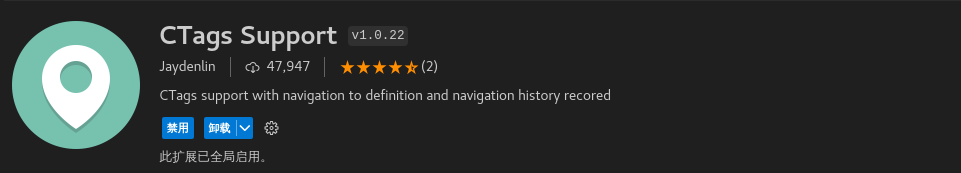

3.4、Ctags Support

3.4.1 插件图标与名称

3.4.2 插件功能

此插件本身不带ctags组件,它只是作为ctags到vscode的桥梁,将两者联系起来,使得vscode中的其他插件能够自动调用ctags相关功能。Ctags组件下载地址

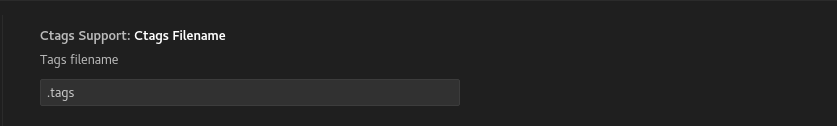

3.4.3 插件用法

右键CTags Support,选择扩展设置,修改为如图所示

3.5、Verilog Highlight

3.5.1 插件图标与名称

3.5.2 插件功能

完善Verilog和System Verilog代码高亮功能

3.5.3 插件用法

无需额外操作,即装即用

3.6、verilog-utils

3.6.1 插件图标与名称

3.6.2 插件功能

完善模块实例化功能

3.6.3 插件用法

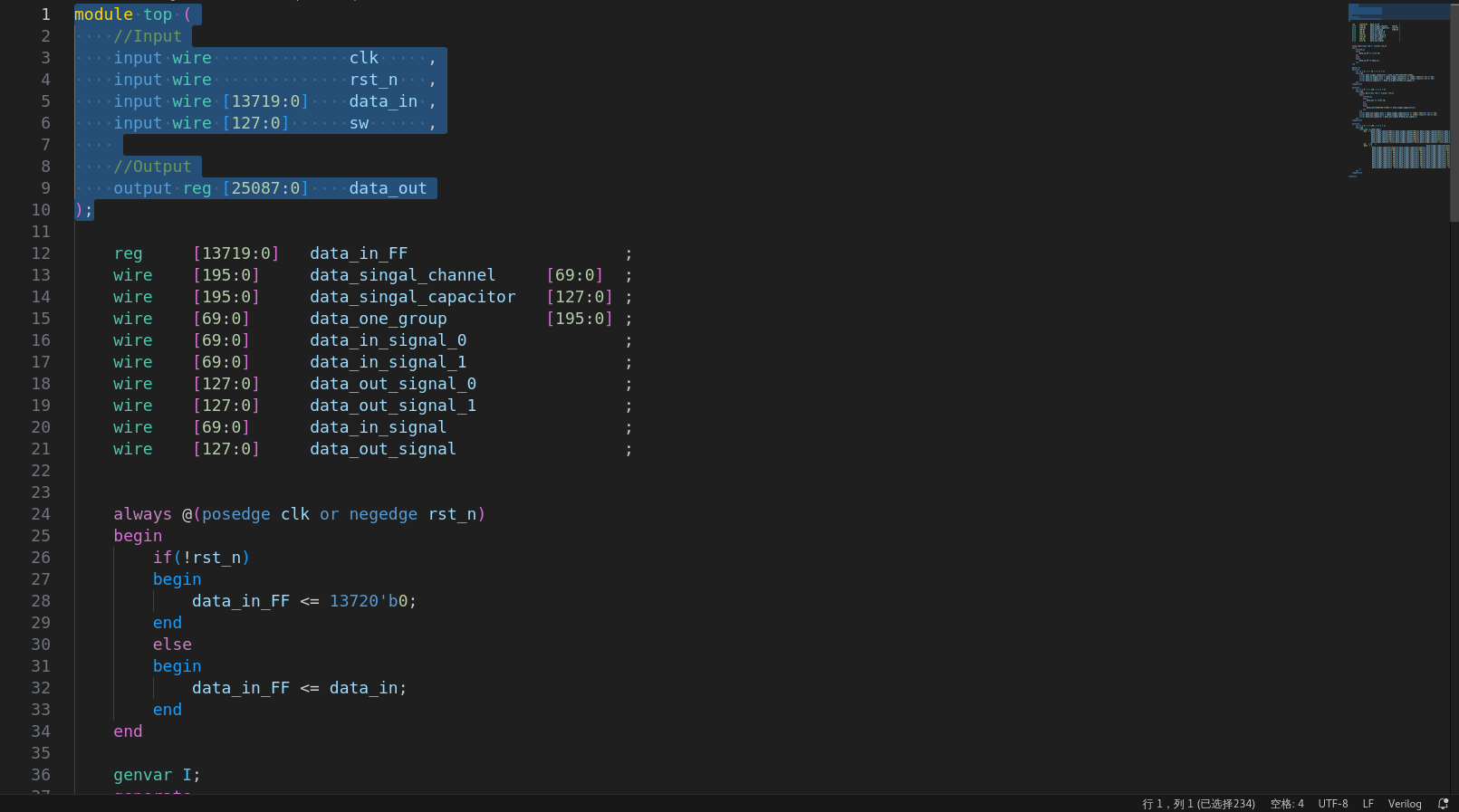

1)选中需要实例化的模块的声明部分

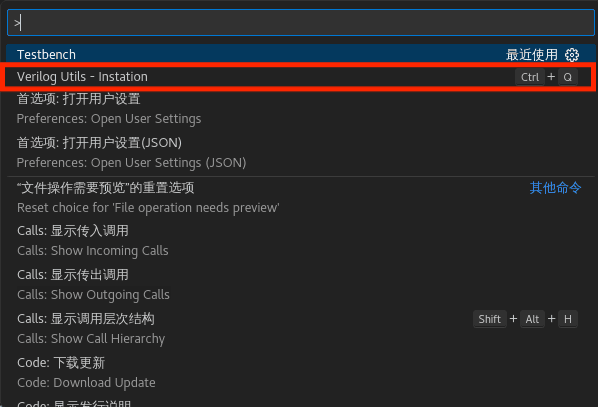

2)按下ctrl + shift + p,打开命令面板,点击Verilog Utils - Instation

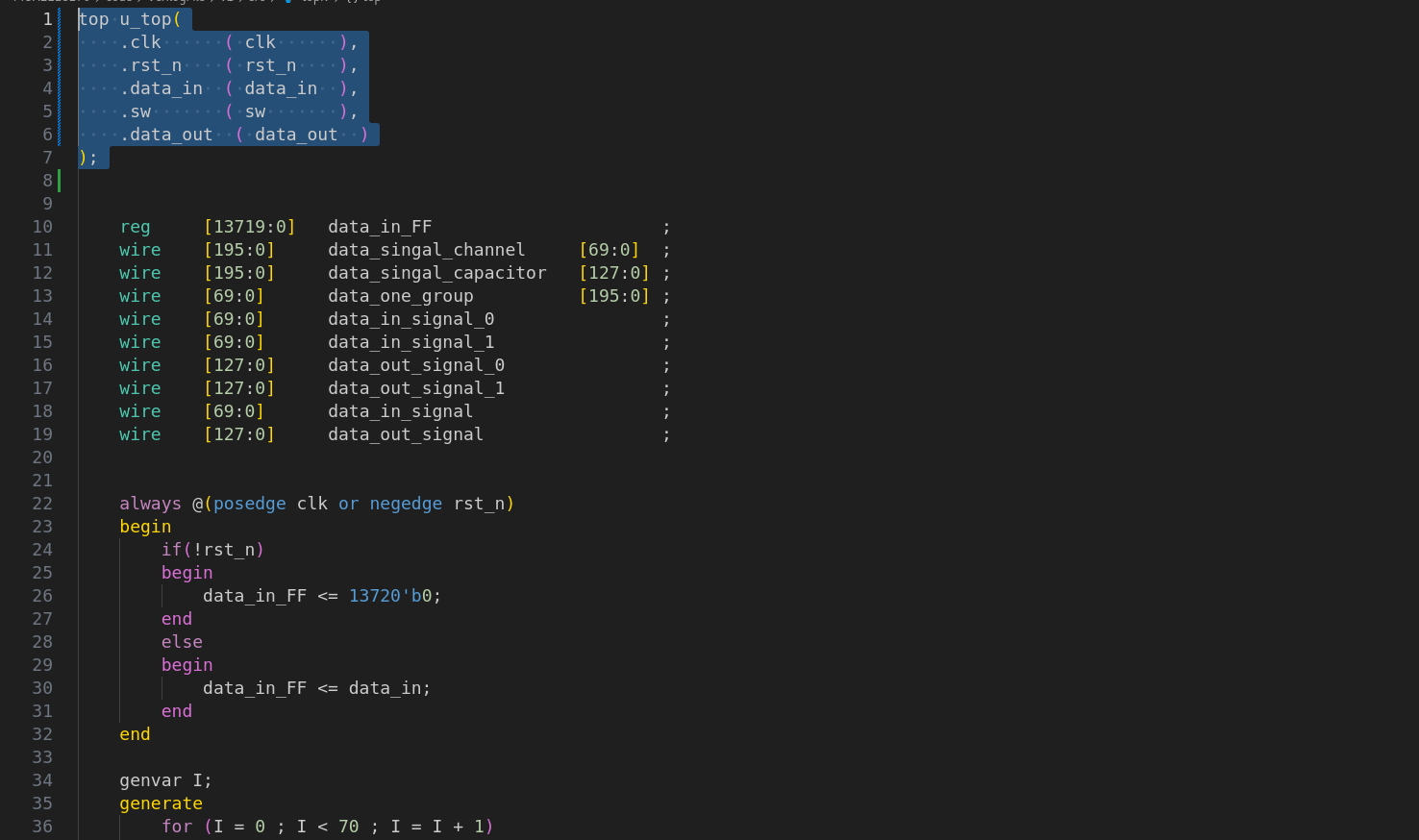

3)这样刚刚选中的模块的实例化就完成了

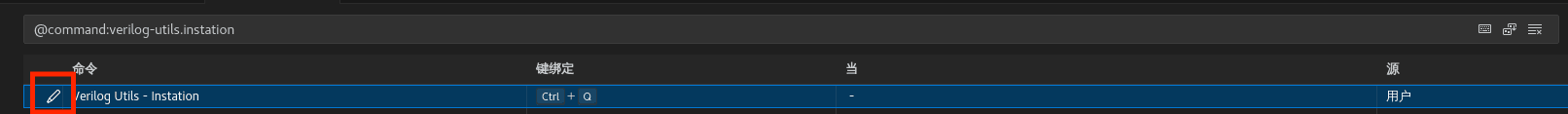

4)我们再次按下ctrl + shift + p,打开命令面板,点击Verilog Utils - Instation选项后面的设置按钮,设置快捷键

5)点击最左边的编辑按钮,记录实例化操作绑定的按键,这里笔主设置的是ctrl + q。这样设置完成后,选中需要实例化的模块声明,按下ctrl + q即可完成实例化

3.7、Verilog_Testbench

3.7.1 插件图标和名称

3.7.2 插件功能

为选中的顶层模块代码生成对应的格式化testbench文件

3.7.3 插件用法

1)配置python3环境

# 用包管理工具yum安装python3

$ sudo yum install python3 -y

# 检查python3版本

$ python3 --version

Python 3.6.8

# 安装后续会用到的插件

$ sudo pip3 install chardet -y

# 打开.bashrc

$ gvim ~/.bashrc

# 因为默认python是2.7版本,而不是我们安装的python3,所以用python3替代python,在.bashrc中加入这么一行代码

alias python="python3"2)在~/.vscode/extensions路径下找到truecrab.verilog-testbench-instance-0.0.5,其结构如图所示

.

├── CHANGELOG.md

├── images

│ ├── fig1.png

│ └── fig2.png

├── out

│ ├── extension.js

│ ├── vInstance_Gen.py

│ └── vTbgenerator.py

├── package.json

├── package-lock.json

├── README.md

├── structure

└── verilog.png3)在该路径下找到out/extensions.js,修改第36行代码

// 原代码

ter1.sendText(`python ${__dirname}\\vTbgenerator.py ${editor.document.fileName}`);

// 修改后代码

ter1.sendText(`python ${__dirname}/vTbgenerator.py ${editor.document.fileName}`);4)随便打开一个verilog文件,按下ctrl + shift + p,打开命令面板,点击testbench,可以看到vscode打开了一个新的名为testbench的终端,运行了这么一行命令,并将testbench的内容打印在终端上

# testbench插件运行的命令

$ python /home/sxc/.vscode/extensions/truecrab.verilog-testbench-instance-0.0.5/out/vTbgenerator.py /home/sxc/IC_prj/SerDes_28nm/MUX_128_70/code/VerilogFile/v1/src/top.v

# 终端打印的信息

//~ `New testbench

`timescale 1ns / 1ps

module tb_top;

// top Parameters

parameter PERIOD = 10;

// top Inputs

reg clk = 0 ;

reg rst_n = 0 ;

reg [13719:0] data_in = 0 ;

reg [127:0] sw = 0 ;

// top Outputs

wire [25087:0] data_out ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

initial

begin

#(PERIOD*2) rst_n = 1;

end

top u_top (

.clk ( clk ),

.rst_n ( rst_n ),

.data_in ( data_in [13719:0] ),

.sw ( sw [127:0] ),

.data_out ( data_out [25087:0] )

);

initial

begin

$finish;

end

endmodule5)到第4步verilog_testbench插件已经能够正常使用了,但是它会新建一个终端并将testbench内容打印在终端里,非常的不方便,所以我们在此基础上稍作修改

# 打开bashrc

$ gvim ~/.bashrc

# 在其中加入下面一段代码

#Verilog Testbench

export vTbgenerator_HOME="~/.vscode/extensions/truecrab.verilog-testbench-instance-0.0.5/out/vTbgenerator.py" #The path to your vTbgenerator

function create_tb {

local DesignTopName=$1 # DesignTopName

local DesignPath=`pwd` # Path

local TbFileName="tb_${DesignTopName}" #TbName

echo ${TbFileName}

echo ${DesignPath}

echo "python3 ${vTbgenerator_HOME} ${DesignPath}/${DesignTopName}.v >> ${DesignPath}/../tb/${TbFileName}.v"

python3 ${vTbgenerator_HOME} ${DesignPath}/${DesignTopName}.v >> ${DesignPath}/../tb/${TbFileName}.v

}

alias create_tb="create_tb"

# 修改完成后保存退出,并source一下.bashrc

$ source .bashrc6)现在我们已经完成修改,下面是一段实例

# 运行create_tb命令前文件夹内容

.

├── src

│ ├── comb_logic_fundamental.v

│ ├── comb_logic.v

│ ├── para.v

│ └── top.v

└── tb

2 directories, 4 files

# 在src目录下运行create_tb top

$ create_tb top

# 运行create_tb命令后文件夹内容

.

├── src

│ ├── comb_logic_fundamental.v

│ ├── comb_logic.v

│ ├── para.v

│ └── top.v

└── tb

└── tb_top.v

2 directories, 5 files生成的tb_top.v中的内容

//~ `New testbench

`timescale 1ns / 1ps

module tb_top;

// top Parameters

parameter PERIOD = 10;

// top Inputs

reg clk = 0 ;

reg rst_n = 0 ;

reg [`WIDTH*`CHANNEL_NUM-1:0] data_in = 0 ;

reg [`CAPACITOR_NUM-1:0] sw = 0 ;

// top Outputs

wire [`WIDTH*`CAPACITOR_NUM-1:0] data_out_FF ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

initial

begin

#(PERIOD*2) rst_n = 1;

end

top u_top (

.clk ( clk ),

.rst_n ( rst_n ),

.data_in ( data_in [`WIDTH*`CHANNEL_NUM-1:0] ),

.sw ( sw [`CAPACITOR_NUM-1:0] ),

.data_out_FF ( data_out_FF [`WIDTH*`CAPACITOR_NUM-1:0] )

);

initial

begin

$finish;

end

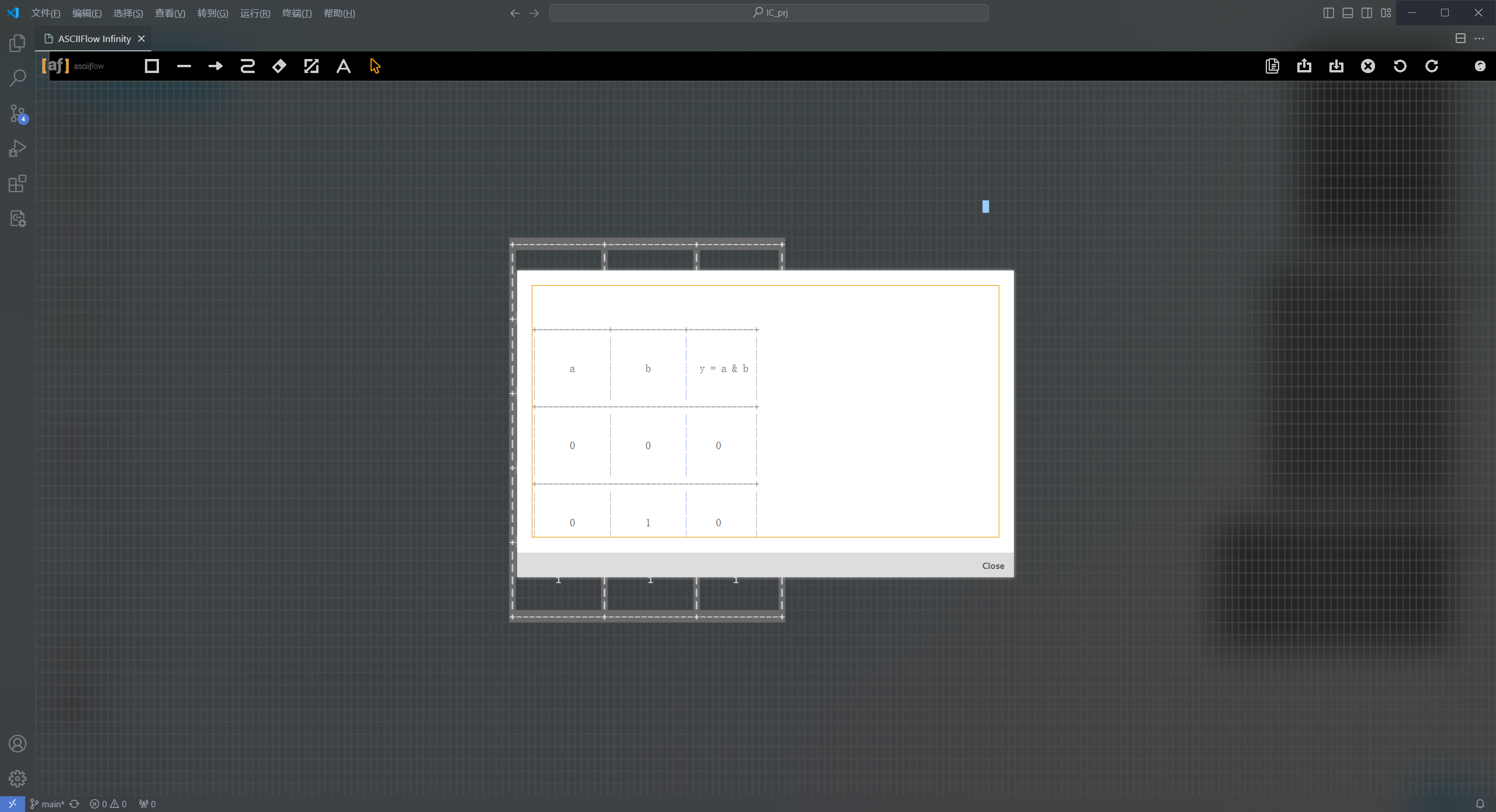

endmodule3.8、Asciiflow2

3.8.1插件图标和名称

3.8.2插件功能

可以用来画注释图,比如一段代码需要用框图来注释的时候,用这个插件会非常方便。

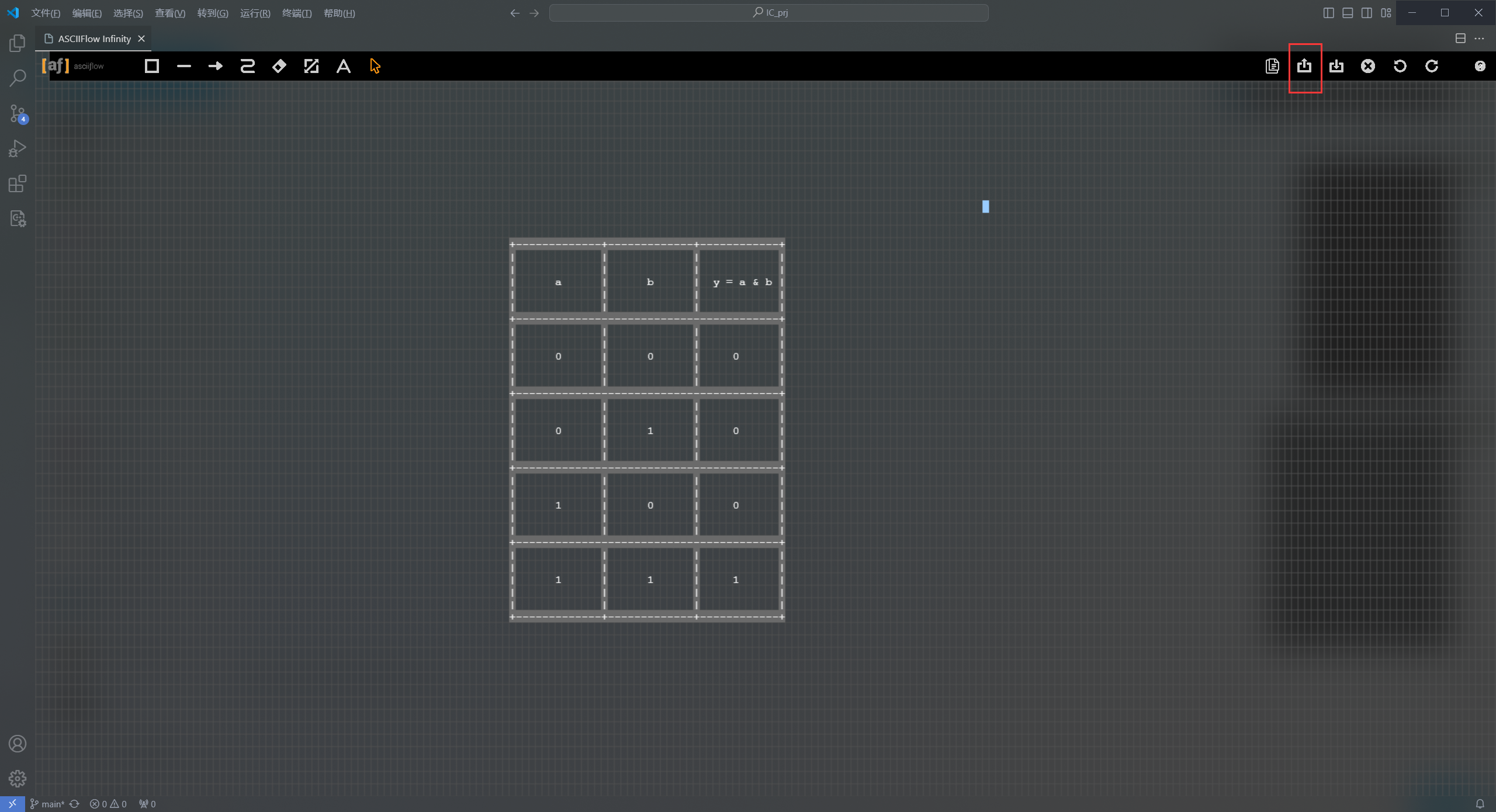

3.8.3插件用法

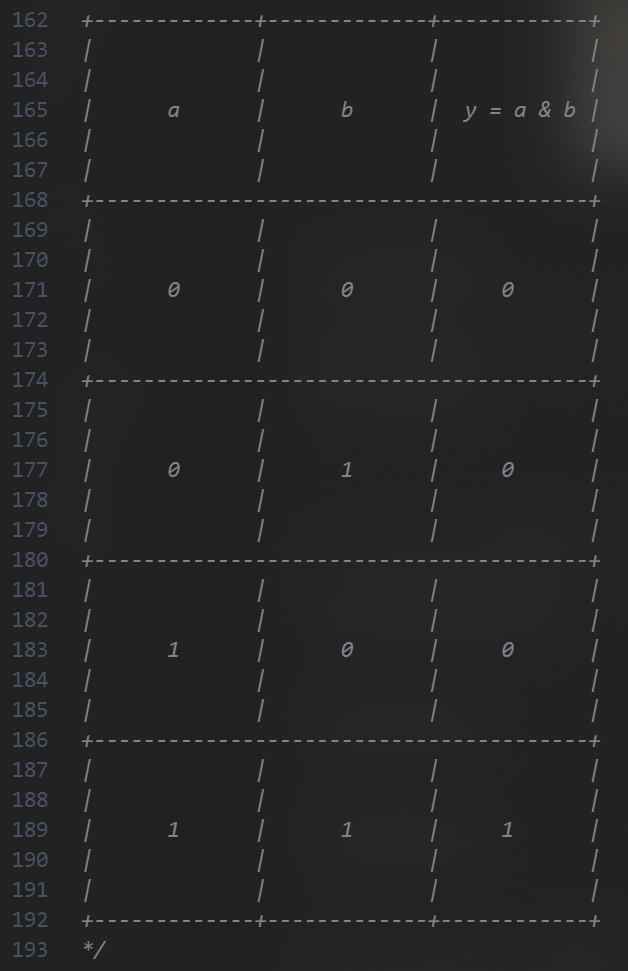

ctrl + shift + p打开功能面板,找到Asciiflow:Open Asciiflow,点击该选项打开。这里以画一个简单的逻辑真值表,逻辑表达式为y = a \and b(这个符号在latex里面是逻辑与),然后点击右上角

export

复制白色方框中的内容粘贴到你的代码片段中即可

最终代码中效果如果所示